- Xilinx verilog tutorial software#

- Xilinx verilog tutorial code#

- Xilinx verilog tutorial license#

- Xilinx verilog tutorial zip#

- Xilinx verilog tutorial simulator#

In such scenarios, the proposed mesochronous FIFO can be extended to support multicycle link delays in a modular manner and with minimal modifications to the baseline architecture. The proposed design can operate correctly even when the transmitter and the receiver are separated by a long link whose delay cannot fit within the target operating frequency. In this brief, we present a novel mesochronous dual-clock first-input– first-output (FIFO) buffer that can handle both clock synchronization and temporary data storage, by synchronizing data implicitly through the explicit synchronization of only the flow-control signals. In such cases, clock synchronization is needed when sending data across modules. Under this regime, the modules at the two ends of a mesochronous interface receive the same clock signal, thus operating under the same clock frequency, but the edges of the arriving clock signals may exhibit an unknown phase relationship. It will start the installation.The Mesochronous Dual-Clock FIFO Buffer - To increase system composability and facilitate timing closure, fully synchronous clocking is replaced by more relaxed clocking schemes, such as mesochronous clocking. The installation will require a lot of time too. Getting Started With Xilinx Vivado W/ Digilent Nexys 4 FPGA 1 - Build Multiple Inputs AND Logic Gate: I do this instructable because it looks like there is not simple getting started tutorial to. Point to be noted – Both the download and extraction will need a lot of time depending upon internet speed and storage availability. After the extraction, the file name should be – ‘Xilinx_ISE_DS_Win_14.7_1015.1”. To unzip the file, right-click on the file, and there will be an option to extract all. You can choose according to your requirement and choice from the below given link. There are other downloadable options available.

Xilinx verilog tutorial zip#

(It is a 6GB ZIP file, ensure internet connection and space) The link for windows – The link to download Xilinx is given below – Choose the location to create New Project.

Xilinx verilog tutorial software#

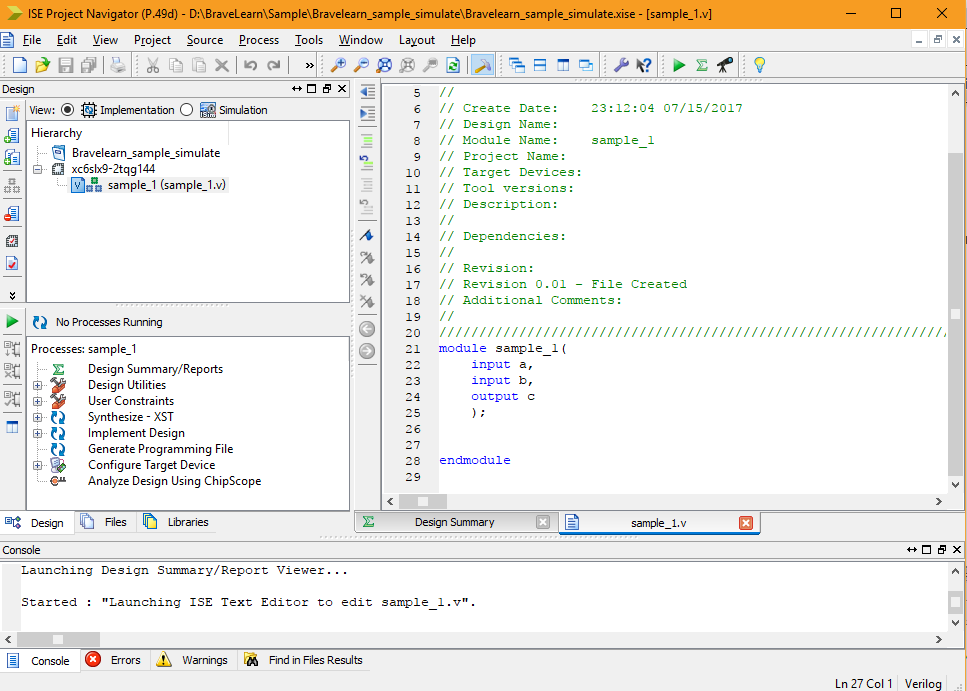

Open the Xilinx ISE Software Open New Project. I think they still do not support windows 8. Xilinx 14.4 has some annoying bugs when run with Windows 8.

Xilinx verilog tutorial code#

Step 1: Download the software from the internet. Verilog code Using Xilinx Software Neeraj Kulkarni neerajkiitk.ac.in.What is VHDL? What is the difference between Verilog & VHDL? Xilinx Installation Process

We are demonstrating this tutorial for windows only.

Xilinx verilog tutorial license#

The license will be mailed in that email-id.

Xilinx verilog tutorial simulator#

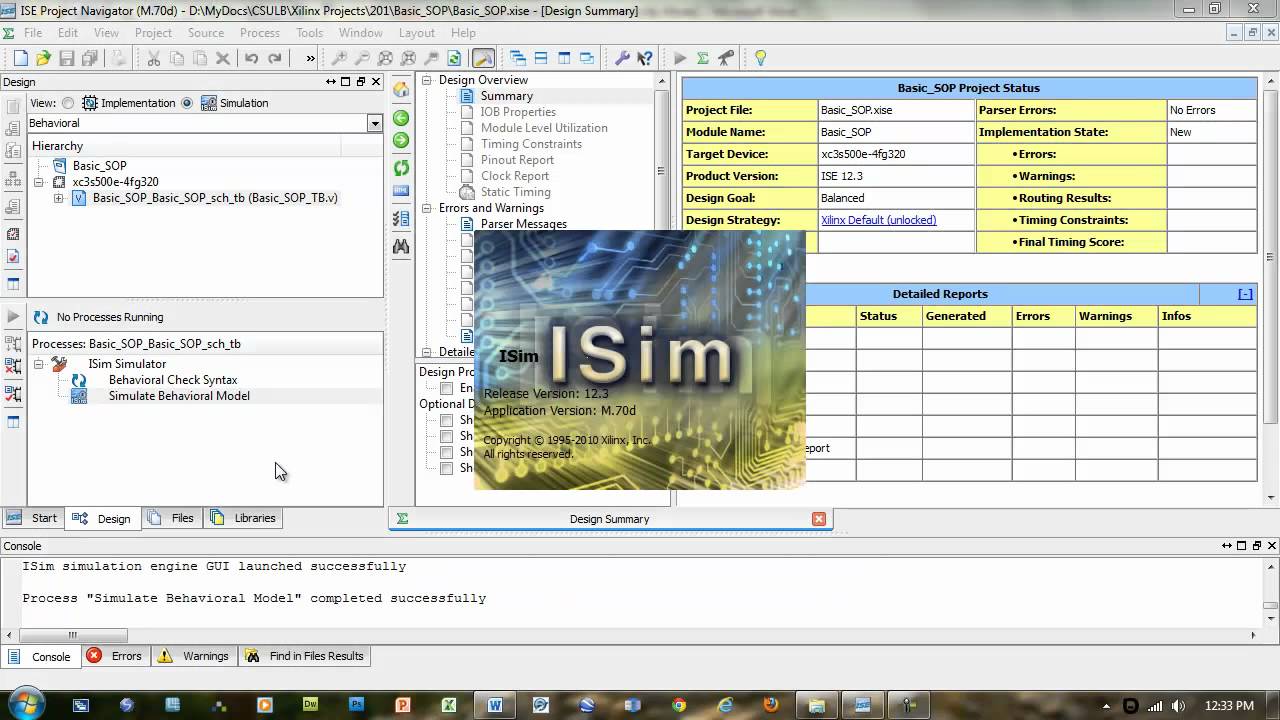

We will use Xilinx’s software “ISE 14.7 Simulator to implement Verilog designs. Xilinx is a USA based tech-company which provides programmable logic devices. Creating your first Verilog project with XILINX XILINX Prerequisites for Verilog HDL Using Xilinxĭ.

0 kommentar(er)

0 kommentar(er)